埋栅型静电感应器件研制中的外延技术

发布时间:2008-11-10阅读:1293

0 引言

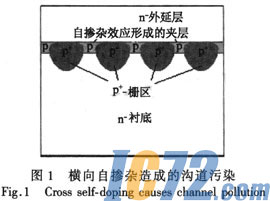

静电感应晶体管SIT是一种结构灵敏的器件,也是具有类真空三极管特性的新型电力半导体器件,一般为常开型器件。从结构上说SIT与一般场效应晶体管FET相似,但沟道更窄、更短,具有其他半导体器件无法比拟的一系列优点,如优异的高频特性和高速开关特性,无电流集中,耐击穿强度高,驱动功率小,属于电压驱动型器件。静电感应晶体管可广泛应用于高速、高压、低功耗场合。就大功率上有高频感应加热,在高频上应用有中波广播发射机,在低功耗应用方面有叉车的速度控制器,在小功率应用方面有显示器CTR的驱动等。另外还有不停电电压、高压特殊电压、超声波清洗机、鱼群探测器等。 在静电感应晶体管研制过程中,发现在关键工艺外延工序中,即在p型衬底上生长n-型高阻外延层时存在自掺杂效应,即热蒸发使衬底p型杂质进入气相,改变了气相中的掺杂成分和浓度,导致外延层中的杂质实际分布偏离理想情况,使生长的外延层或者低阻化为n+型,或者反型为p型层,或者可能出现不希望的夹层,从而改变器件结构(如图1所示),影响器件性能,最终导致器件研制失败。本研究中,外延工序主要解决两个问题:一是保证使外延层高阻化;二是防止自掺杂效应引起的Si片反型。

|

|

1 高阻外延中方块电阻的控制

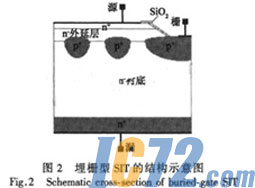

电力埋栅型静电感应晶体管SIT的单元截面图如图2所示。图中可以看出,所需要的外延层为高阻n-型,设计厚度为10~16μm,首先从结构上保证了栅源击穿电压可达到几十伏的数量级。除外延层厚度外,影响栅源击穿电压的主要是外延层方块电阻的大小。

|

|

对单边突变平行平面结,雪崩击穿电压VB可表示为

![]()

式中,N为外延层的掺杂浓度。实际的击穿电压比理论值小,经常使用的经验求算公式有

式中,ρ为高阻区的电阻率。击穿时对应的耗尽层宽度为

![]()

对栅-外延层结来说,由于外延层厚度较小,该结击穿电压实际是穿通击穿,此时击穿电压VPT与外延层厚度dep的关系为

![]()

由此可以估计一定外延层电阻率和外延层厚度下对应的栅源击穿电压。

图3给出了外延层厚度为10μm、外延方块电阻在100~100 000 Ω/□的结果。可以看出,从理论上说外延方块电阻控制在几千到几万Ω/□比较合适,相应电阻率为几个Ω·cm到几十Ω·cm。外延后由于后继工艺造成的栅体杂质再扩、源区扩磷侵蚀等因素影响,最终外延层有效厚度将不足10μm,图4给出了外延层厚度在5~10μm时不同外延层电阻率对应的击穿电压。考虑到后继工序对外延层侵蚀,外延电阻率在8~20 Ω·cm为宜,即最佳外延层方块电阻控制在4 000~10 000Ω/□较合适。

|

2 外延中的自掺杂及其解决办法

对于SIT,自掺杂效应主要来源于浓硼扩散形成的栅区中的硼原子在外延层中的反扩散。根据现有条件,需要采用各种方法,减少外延前预烘焙过程中从栅体蒸发的杂质,保证外延过程不反型。本文采用的方法主要是补偿法,包括背封法、两步外延法和染磷法,并通过实验验证了这些方法是有效、合理的。

2.1 背封技术

外延过程中,杂质从衬底背面的蒸发和背面的反向腐蚀效应是导致自掺杂的一个重要原因。为了控制自掺杂、避免外延层反型和提高方块电阻,可以采用背封技术,用高纯Si或SiO2等薄膜把衬底表面封闭起来。具体的背封措施通常采用生长SiO2的办法来封住背面,防止杂质挥发。背封的缺点是不可避免的引入了热应力,导致后工序的碎片率上升。经过实验,采用此方法得到的外延层方块电阻为4 000~5 000 Ω/□,管芯外延层类型为n型。

2.2两步外延法

外延生长过程中,掺杂剂引入的杂质和自掺杂引入的杂质,都会掺入外延层。外延补偿的思路是通过调控外延过程中掺杂剂的掺杂百分数,对自掺杂引入的杂质进行补偿,使外延层杂质浓度、电阻率达到预期值。

随着外延层厚度的逐渐增加,埋栅表面杂质蒸发引起的自掺杂的影响逐渐减小,所以其影响主要在外延生长的初始阶段。为了得到合格的外延层,工艺中采用了两步外延的方法,即首先用重掺杂生长,对栅体表面蒸发出来的p型杂质进行充分补偿;待外延层生长到一定厚度,栅体表面蒸发出来的p型杂质的影响很小时,再改用本征生长,直到生长到所需的厚度。

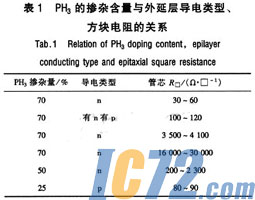

两步外延的具体工艺中要注意的是重掺杂的浓度和厚度:重掺杂补偿后、外延再生长前,外延层表面可能的导电类型为p、p-、n-或者n型,为得到高质量、高阻外延层,最好是p-、n-型。也就是说初次外延后的表面杂质浓度控制在5×1014 cm-3(p型)~5×1014cm-3(n型)。多次实验表明,若外延层厚度约为10 μm,外延方块电阻为5 000~20 000 Ω/□,则第一步外延以PH3掺杂70%为宜,生长厚度控制在1μm左右。具体时间和厚度,由外延生长条件和外延过程中的具体操作步骤决定,以二次外延正式生长前、各热处理完成后,被覆盖的栅体表面的B不至于外溢到表面为前提。但控制掺PH3的量是一个难题。从表1中可以看出,如果量太多,所得到的基本上是低阻外延,和所要求的高阻外延相差很多,且R□的随机性很大,时高时低;减少PH3的掺杂含量,又出现了反型的情况。鉴于外延工艺调节的困难,经过大量实验后,提出外延前的染磷技术。即采用外延前补偿,外延时只本征生长,这就是外延前的染磷工艺。

|

|

对于SIT来说栅体表面蒸发出来的杂质是最主要的,而对SITH来说除了栅体表面蒸发出来的杂质,还有背面阳极蒸发出来的p型杂质的影响也是不容忽略的,这就是为什么SITH在外延过程中比SIT更容易反型的原因。

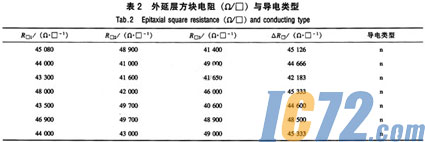

两步外延法是在外延环节中用重掺杂的方法把栅体表面蒸发出来的p型杂质进行充分补偿,而扩散染磷法则是在进行外延之前,用扩散方法把SIT、SITH的栅体和SITH的阳极表面用一层薄薄的浓磷层盖住,这样在外延的过程中,该层薄磷层能阻止p型杂质的挥发,又能在外延时同栅体表面的p型杂质同时蒸发出来,相互之间进行补偿,这样就可以得到所预期的外延层。经过多次试验,确定染磷的具体工艺为:在930~950℃下,在扩散炉内用氧气携带液态POCl3对Si片扩散10 min。相对应的外延工艺采用的是:在1180℃下,在外延炉内对Si片反复吹H2和本征生长单晶Si。这里需要指出的是,吹H2的目的主要是将外延气氛中除H2外的所有有害气体吹出反应室,包括由于热蒸发而外溢出的杂质气体。吹H2的时间是由试炉的结果(即试片的方块电阻)而定。一般来说,若试片的方块电阻合适或偏大则不吹H2;若试片的方块电阻偏小,则增加正式投片的吹H2时间。下面表2所列出的外延数据显示用扩散染磷法对于提高外延层的方块电阻和防止外延层反为p型很有效果。表2中,△R□为平均值。

|

|

实践证明,染磷法外延是可行的,对制管中外延工艺有很大帮助。这种方法用重掺杂的方法把栅体表面蒸发出来的p型杂质进行充分补偿的过程放到了扩散工序,相对于两步外延方法来说,避免了两步外延中工序复杂、工艺周期长和不宜大量生产的缺点,简化了工艺,用较少的炉次就可以做出合格的外延片,缩短了制管时间,降低了生产成本。实验证明,这种外延方法结合SITH背面阳极腐蚀工艺,能够做出特性良好的管子。